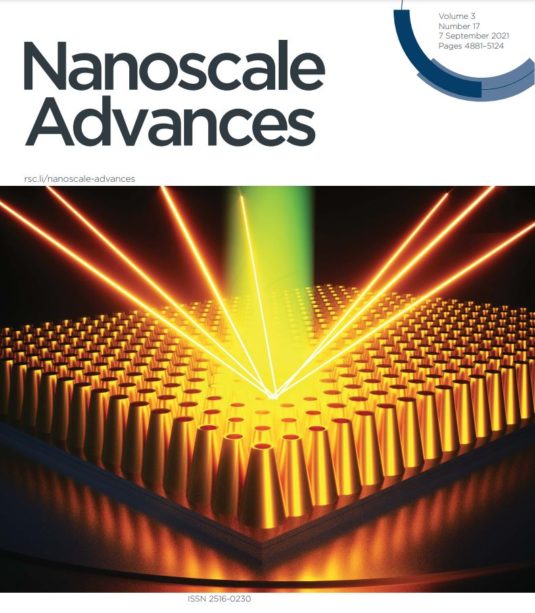

A wafer-scale fabrication method for threedimensional plasmonic hollow nanopillars

A wafer-scale fabrication method for threedimensional plasmonic hollow nanopillars

D. Jonker (UT), Z. Jafari, J. P. Winczewski, C. Eyovge, J. W. Berenschot,

N. R. Tas, J. G. E. Gardeniers, I. De Leon and A. Susarrey-Arce

MCEC PhD Dirk Jonker‘ (UT) publication reports on the fabrication and modification of a top-down nanofabrication platform for enormous parallel silicon nanowire-based devices. In they paper the authors explain the nanowire formation in detail, using an additive hybrid lithography step, optimising a reactive ion etching recipe for obtaining smooth and vertical nanowires under a hybrid mask, and embedding the nanowire in a dielectric membrane.